Proceedings of the 14th USENIX Symposium on Operating Systems Design and Implementation (OSDI '20)

November 4–6, 2020

## conference

proceedings

## **14th USENIX Symposium on Operating Systems Design and** Implementation (OSDI '20)

*November* 4–*6, 2020*

Sponsored by

In cooperation with ACM SIGOPS

**Industry Partners and Media Sponsor**

ACM Queue DMTF FreeBSD Foundation

## **USENIX Supporters**

## **USENIX** Patrons

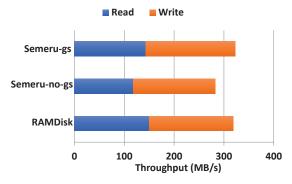

Bloomberg • Facebook • Google Microsoft • NetApp

## **USENIX Benefactors**

Amazon • AuriStor • Oracle Thinkst Canary • Two Sigma • VMware

## **USENIX Partners**

Top10VPN

## **Open Access Publishing Partner**

PeerJ

**USENIX** Association

# Proceedings of the 14th USENIX Symposium on Operating Systems Design and Implementation (OSDI '20)

November 4–6 2020

#### © 2020 by The USENIX Association

#### All Rights Reserved

This volume is published as a collective work. Rights to individual papers remain with the author or the author's employer. Permission is granted for the noncommercial reproduction of the complete work for educational or research purposes. Permission is granted to print, primarily for one person's exclusive use, a single copy of these Proceedings. USENIX acknowledges all trademarks herein.

#### ISBN 978-1-939133-19-9

Cover Image created by freevector.com and distributed under the Creative Commons Attribution-ShareAlike 4.0 license (https://creativecommons.org/licenses/by-sa/4.0/).

#### Symposium Organizers

#### **Program Co-Chairs**

Jon Howell, *VMware Research* Shan Lu, *University of Chicago*

#### **Program Committee**

Rachit Agarwal, Cornell University Lorenzo Alvisi, Cornell University Tom Anderson, University of Washington Sebastian Angel, University of Pennsylvania Andrea Arpaci-Dusseau, University of Wisconsin-Madison Andrew Baumann, Microsoft Research Irina Calciu, VMware Research George Candea, EPFL Rong Chen, Shanghai Jiao Tong University Wenguang Chen, Tsinghua University Vijay Chidambaram, The University of Texas at Austin and VMware Research Byung-Gon Chun, Seoul National University Allen Clement Natacha Crooks, University of California, Berkeley Dilma Da Silva, Texas A&M University Alexandra Fedorova, University of British Columbia Jason Flinn, Facebook Roxana Geambasu, Columbia University Yossi Gilad, The Hebrew University of Jerusalem Haryadi Gunawi, University of Chicago Andreas Haeberlen, University of Pennsylvania Tim Harris, Amazon Chris Hawblitzel, Microsoft Research Gernot Heiser, University of New South Wales and CSIRO's Data61 Y. Charlie Hu, Purdue University Ryan Huang, Johns Hopkins University Rebecca Isaacs. Twitter Frans Kaashoek, Massachusetts Institute of Technology Manos Kapritsos, University of Michigan Baris Kasikci, University of Michigan Kimberly Keeton Anne-Marie Kermarrec, EPFL Ana Klimovic, Google Research and ETH Zurich Jinyang Li, New York University Wyatt Lloyd, Princeton University Jay Lorch, Microsoft Research

Xiaosong Ma, Quatar Computing Research Institute Kathryn S. McKinley, Google James Mickens, Harvard University Robert Morris, Massachusetts Institute of Technology Derek Murray, Google Madan Musuvathi, Microsoft Research Bryan Parno, Carnegie Mellon University Simon Peter, The University of Texas at Austin Don Porter, The University of North Carolina at Chapel Hill Dan Ports, Microsoft Research Costin Raiciu, University Politehnica of Bucharest Malte Schwarzkopf, Brown University Ryan Stutsman, University of Utah Michael Swift, University of Wisconsin-Madison Kaushik Veeraraghavan, Facebook Rashmi Vinayak, Carnegie Mellon University Xi Wang, University of Washington Yang Wang, The Ohio State University John Wilkes, Google Emmett Witchel, The University of Texas at Austin Harry Xu, University of California, Los Angeles Tianyin Xu, University of Illinois at Urbana-Champaign Junfeng Yang, Columbia University Ding Yuan, University of Toronto Nickolai Zeldovich, Massachusetts Institute of Technology Irene Zhang, Microsoft Research Yiying Zhang, University of California, San Diego Lidong Zhou, Microsoft Research Yuanyuan Zhou, University of California, San Diego

#### **Steering Committee**

Andrea Arpaci-Dusseau, University of Wisconsin—Madison Jason Flinn, Facebook Casey Henderson, USENIX Association Kimberly Keeton Hank Levy, University of Washington James Mickens, Harvard University Brian Noble, University of Michigan Timothy Roscoe, ETH Zurich Margo Seltzer, University of British Columbia Geoff Voelker, University of California, San Diego

#### **External Reviewers**

Joy Arulraj Mahesh Balakrishnan Fred Chong Peter Chubb Zhihao Jia Gerwin Klein Jing Li Ashlie Martinez Justin Meza Rajesh Nishtala Rohan Padhye Mark Silberstein

Adriana Szekeres Chunqiang Tang Carl Waldspurger Ben Y. Zhao

## Message from the OSDI '20 Program Co-Chairs

#### Dear colleagues,

Welcome to the 14th USENIX Symposium on Operating Systems Design and Implementation (OSDI '20)!

This year's program offers an unprecedented 70 exceptional papers. These papers represent the many strengths of our community and cover a wide range of topics, including file and storage systems, networking, scheduling, security, formal verification of systems, cluster management, system support for machine learning, hardware, consistency, consensus protocols, debugging, and, of course, operating systems design and implementation.

Our committee received a bumper crop of 400 submissions, an increase of more than 50% over OSDI '18. This growth demanded that we modify the review process and grow the committee at the last minute to handle the load. When you bump into a PC member, give them a huge thank you! Sixty-five members participated, including academics, industrial researchers, and industrial practitioners. Papers received two reviews in the first round; 305 advanced to round two, where they received an additional review. Of those, 177 advanced to round three, where they received three more reviews. For a small number of papers, where opinions were divided or where a paper was particularly specialized, we solicited additional expert reviews. In total, the PC and external reviewers wrote more than 1.6 million words in more than 1,600 thoughtful reviews.

After a rigorous online discussion across the full PC, the heavy PC members discussed 101 papers in a virtual 2-day PC meeting. The PC chairs strove to ensure that all the discussed papers received full and fair consideration, coming to a consensus agreement in almost every case. Papers were placed into high-level categories according to their main topic so that similar papers could be discussed together at the PC meeting. All discussed papers received a summary of the PC discussion written by a heavy PC member. In the end, the PC selected 70 papers for presentation at the conference, resulting in an 18% acceptance rate, similar to prior years. Each of the accepted papers was allocated an additional two pages and shepherded by a member of the heavy PC to help the authors address the reviewers' comments in their camera-ready versions.

After finalizing the program, we created a separate committee to decide the Jay Lepreau Best Paper Awards composed of PC members with no conflicts with the papers under consideration. PC members nominated papers for these awards. We selected four papers with at least two nominations for best paper as candidates for the award. After reading the nominated papers and considering the reviews from the full PC, the awards committee agreed on three Jay Lepreau Best Paper Awards.

As PC co-chairs, we stand on the shoulders of so many who did a tremendous amount of hard work to make OSDI '20 a success. First, we thank the authors of all submitted papers for choosing to send their work to OSDI. Thanks also to the program committee for their hard work in reviewing and discussing the submissions and in shepherding the accepted papers. We thank Vijay Chidambaram and James Mickens for organizing the Ask Me Anything sessions, and we thank Malte Schwarzkopf, Aastha Mehta, Natacha Crooks, and Brian Noble for organizing the student mentoring sessions. We are delighted that Anjo Vahldiek-Oberwagner, Eric Eide, and Ryan Stutsman have organized the artifact evaluation process. We are also grateful to the external reviewers who provided additional perspectives. We thank the USENIX staff, who have been fundamental in organizing to our speakers, asking challenging and insightful questions, sharing your ideas with others, and networking with one another in Slack!

We hope you will find OSDI '20 interesting, educational, and inspiring!

Shan Lu, *University of Chicago* Jon Howell, *VMware* OSDI '20 Program Co-Chairs

## Message from the OSDI '20 Artifact Evaluation Committee Co-Chairs

It is our pleasure to report on the artifact evaluation process conducted as part of OSDI '20. This year's conference represents the first time that OSDI has included an artifact evaluation committee (AEC), and it immediately follows the inaugural year for artifact evaluation at SOSP.

The goal of artifact evaluation is to incentivize authors to invest in the broader scientific community by producing artifacts that illustrate their claims, enable others to validate those claims, and accelerate future scientific progress. A paper with artifacts that have passed the artifact evaluation process is recognized in two ways: first by badges that appear on the paper's first page, and second by an appendix that details the artifacts.

#### Process

In designing the artifact evaluation process for OSDI, we aimed to bridge the processes from earlier USENIX conferences (USENIX Security) and the prior effort from ACM SOSP. USENIX previously used a single-badge process, whereas SOSP used a system based on the ACM's artifact review and badging policy. After deliberation, we decided on a three-badge approach to evaluation. This helps establish congruence between the processes for SOSP and OSDI, and the finer granularity of a multi-badge system encourages participation even when full artifacts cannot be shared or specific results are too challenging for the committee to reproduce. The three badges that we used for OSDI are:

- Artifacts Available: Have the artifacts associated with the paper been made available for retrieval both permanently and publicly?

- Artifacts Functional: Do the artifacts conform to the expectations set by the paper in terms of functionality, usability, and relevance?

- Results Reproduced: Can the AEC use the submitted artifacts to obtain the main results presented in the paper?

The criteria for each badge are independent; for example, an artifact does not need to be deemed available or functional in order to be considered for the "Results Reproduced" badge. The third badge corresponds to the "Results Replicated" badge at SOSP '19 but differs in name. The OSDI badge name matches terminology recommended by the National Information Standards Organization (NISO).

#### Evaluation

To form the artifact evaluation committee, we issued an open invitation to the systems community for self-nominations. From the self-nominations, we selected 40 early-career researchers and graduate students based on their levels of expertise.

After the decisions for OSDI '20 paper submissions were distributed, the authors of accepted papers were invited to submit artifacts for evaluation. (Thus, the artifact evaluation process had no effect on which papers were chosen to appear at OSDI.) Authors had one and a half weeks, until August 28, to respond to the call for artifacts. At artifact-submission time, authors were required to choose the badges for which their submission would be considered. The overwhelming majority of submissions applied for all three badges. Each artifact was accompanied by the accepted version of its associated paper so that the AEC could evaluate each artifact against its paper's claims.

A total of 49 artifacts were submitted for evaluation. The AEC members bid on artifacts, and we assigned two or three reviewers for each submission—three if the submission applied for the "Results Reproduced" badge, and two otherwise. After bidding, the AEC had five weeks, until October 9, to make judgments.

Evaluation started with an attempt to build the artifact (where appropriate). Next, AEC members tried to repeat some or all of the experiments described in the artifact's paper. AEC members were cognizant that it would be difficult to reproduce certain reported results, e.g., due to environmental or time limits. Reviewers were able to communicate with authors and regularly did so for clarifications and for help in debugging issues, with HotCRP preserving single-blind reviewing. Along the way, AEC members assessed each artifact's completeness, documentation, and apparent ease of reuse. After all reviews were submitted, the AEC held an online discussion to decide if—for each artifact—it met, exceeded, or fell below the expectations set by its paper.

Overall, the process generated 133 reviews and 1,180 comments with an average of about 3,000 words of combined review text and comments per artifact.

#### Results

OSDI '20 accepted 70 papers; in comparison, SOSP '19 accepted 38. Correspondingly, we received a greater number of submitted artifacts: 49 versus 23. We also saw an increase in the fraction of papers that chose to participate: 70%, up from 61% at SOSP '19. We hope that this trend will continue as artifact evaluation becomes a regular part of our community's conferences.

Of the 49 submitted artifacts, the AEC found that 48 met or exceeded expectations for at least one of the three badges. Per the choices of the authors, not all artifacts were considered for all badges.

- 47 artifacts received the Artifacts Available badge (96%).

- 46 artifacts received the Artifacts Functional badge (94%).

- 39 artifacts received the **Results Reproduced** badge (80%).

The papers that describe these artifacts can be easily recognized by the USENIX artifact evaluation badges that appear on their initial pages.

#### Takeaways

**Cloud Resources:** Increasingly, systems papers present experimental results that depend on large-scale pools of resources for reproduction. Based on feedback from the SOSP '19 efforts, we sought out resources to evaluate these types of artifacts, and Microsoft generously donated resource credits for running artifacts on Azure to help with this issue. Unfortunately, these resources were hard to leverage for the artifacts for which they would have been most useful. Several artifacts relied on access to high-end GPU resources; allocating these resources in Azure requires special approval and quota increases, which we were not able to secure. In some cases, the authors of these artifacts were able to provide reviewers with access to pre-existing resources that the AEC could use for reproduction. In the future, it may make sense to secure quotas for the use of specialized resources (specific GPUs, for example) before the start of the artifact evaluation process, based on types of resources required in the set of accepted papers.

**Single vs. Multiple Badges:** Of the 48 papers that received badges, 11 papers received a subset of the three available badges. We believe this is a strong outcome in favor of the multi-badge badge process we used. If we had opted to use a single badge that encompassed all of our evaluation criteria, it is likely that fewer papers would have received that badge, and consequently, fewer high-quality systems artifacts would have been recognized and documented.

#### Closing

We thank the authors of the 49 submitted artifacts for their hard work in creating these valuable accompaniments to their papers. We also thank the 40 AEC members, who collectively spent hundreds of hours evaluating and discussing these artifacts. Finally, we thank Microsoft for their generous support of the AEC through Microsoft Azure credits. Our hope is that the AEC effort has strengthened the work of the authors who participated, and that it will help facilitate work that builds on the papers that appear in the OSDI '20 proceedings.

The full results and badging for OSDI '20, as well as reports from other artifact evaluation processes within the systems community, can be found online at sysartifacts.github.io.

Eric Eide, University of Utah Ryan Stutsman, University of Utah Anjo Vahldiek-Oberwagner, Intel Labs OSDI '20 Artifact Evaluation Committee Co-Chairs

## OSDI '20: 14th USENIX Symposium on Operating Systems Design and Implementation

## November 4–6, 2020

### Wednesday, November 4

#### Correctness

| Theseus: an Experiment in Operating System Structure and State Management       1         Kevin Boos, Rice University; Namitha Liyanage, Yale University; Ramla Ijaz, Rice University; Lin Zhong, Yale University |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>RedLeaf: Isolation and Communication in a Safe Operating System</b>                                                                                                                                            |

| Specification and verification in the field: Applying formal methods to BPF just-in-time compilers in the Linux kernel                                                                                            |

| Luke Nelson, Jacob Van Geffen, Emina Torlak, and Xi Wang, University of Washington                                                                                                                                |

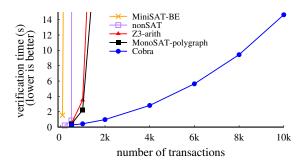

| COBRA: Making Transactional Key-Value Stores Verifiably Serializable                                                                                                                                              |

| <b>Determinizing Crash Behavior with a Verified Snapshot-Consistent Flash Translation Layer</b>                                                                                                                   |

| <b>Storage Systems are Distributed Systems (So Verify Them That Way!)</b>                                                                                                                                         |

| Storage                                                                                                                                                                                                           |

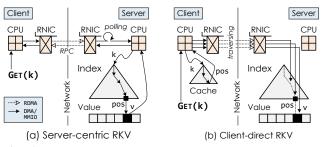

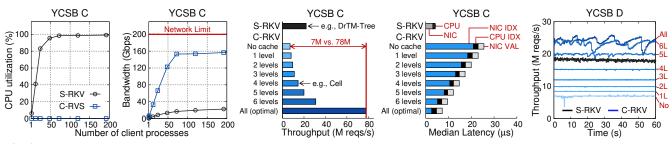

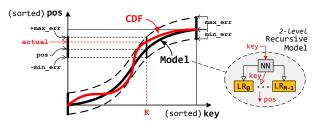

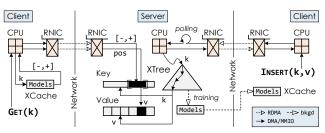

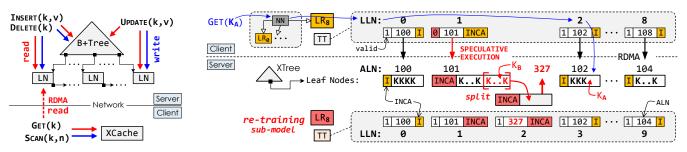

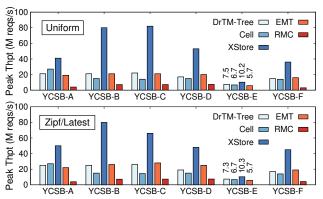

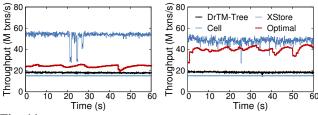

| Fast RDMA-based Ordered Key-Value Store using Remote Learned Cache117Xingda Wei, Rong Chen, and Haibo Chen, Shanghai Jiao Tong University                                                                         |

| CrossFS: A Cross-layered Direct-Access File System                                                                                                                                                                |

| From WiscKey to Bourbon: A Learned Index for Log-Structured Merge Trees                                                                                                                                           |

| LinnOS: Predictability on Unpredictable Flash Storage with a Light Neural Network                                                                                                                                 |

| A large scale analysis of hundreds of in-memory cache clusters at Twitter                                                                                                                                         |

| Generalized Sub-Query Fusion for Eliminating Redundant I/O from Big-Data Queries                                                                                                                                  |

| OS & Networking                                                                                                                                                                                                   |

| A Simpler and Faster NIC Driver Model for Network Functions                                                                                                                                                       |

| PANIC: A High-Performance Programmable NIC for Multi-tenant Networks                                                                                                                                              |

Anirudh Sivaraman, New York University (NYU); Aditya Akella, University of Wisconsin - Madison

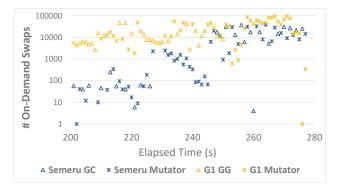

| Semeru: A Memory-Disaggregated Managed Runtime       261         Chenxi Wang, Haoran Ma, Shi Liu, and Yuanqi Li, UCLA; Zhenyuan Ruan, MIT; Khanh Nguyen, Texas A&M University;         Michael D. Bond, Ohio State University; Ravi Netravali, Miryung Kim, and Guoqing Harry Xu, UCLA                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

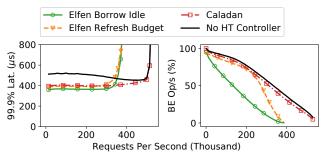

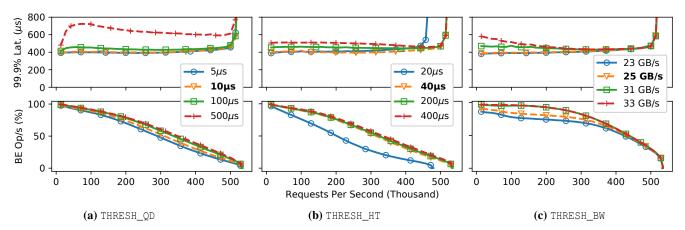

| Caladan: Mitigating Interference at Microsecond Timescales       281         Joshua Fried and Zhenyuan Ruan, <i>MIT CSAIL</i> ; Amy Ousterhout, <i>UC Berkeley</i> ; Adam Belay, <i>MIT CSAIL</i>                                                                                                                                                    |

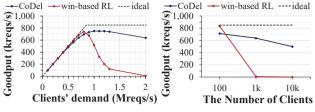

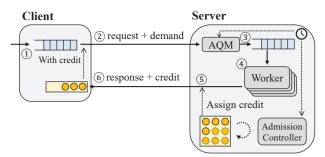

| Overload Control for μs-scale RPCs with Breakwater       299         Inho Cho, Ahmed Saeed, Joshua Fried, Seo Jin Park, Mohammad Alizadeh, and Adam Belay, MIT CSAIL                                                                                                                                                                                 |

| AIFM: High-Performance, Application-Integrated Far Memory                                                                                                                                                                                                                                                                                            |

| Consistency                                                                                                                                                                                                                                                                                                                                          |

| Performance-Optimal Read-Only Transactions       333         Haonan Lu, Princeton University; Siddhartha Sen, Microsoft Research; Wyatt Lloyd, Princeton University                                                                                                                                                                                  |

| Toward a Generic Fault Tolerance Technique for Partial Network Partitioning351Mohammed Alfatafta, Basil Alkhatib, Ahmed Alquraan, and Samer Al-Kiswany, University of Waterloo, Canada                                                                                                                                                               |

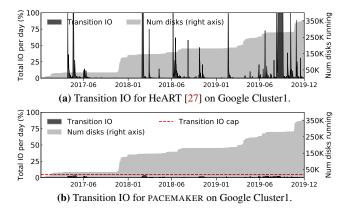

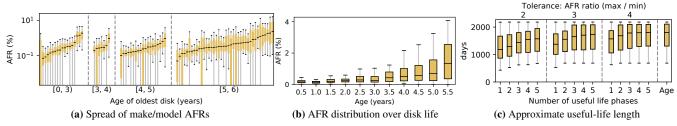

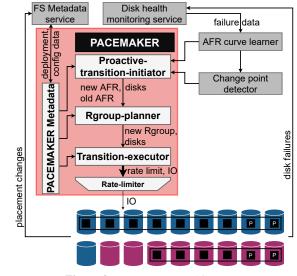

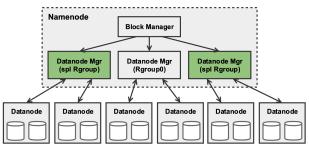

| <i>PACEMAKER</i> : Avoiding HeART attacks in storage clusters with disk-adaptive redundancy                                                                                                                                                                                                                                                          |

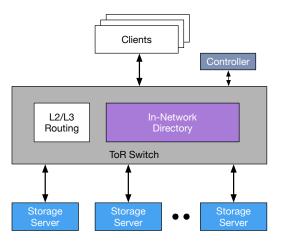

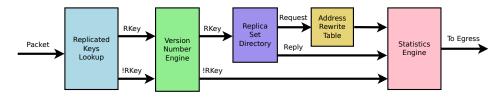

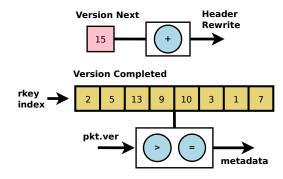

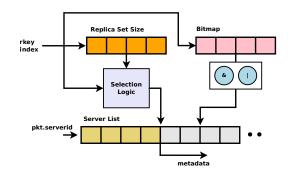

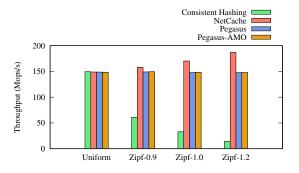

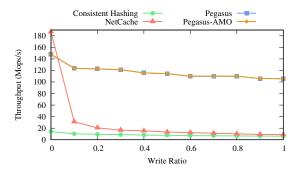

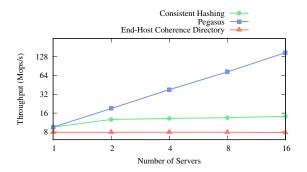

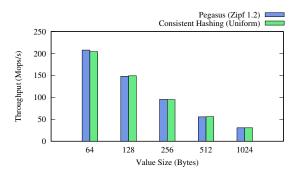

| <b>Pegasus: Tolerating Skewed Workloads in Distributed Storage with In-Network Coherence Directories 387</b><br>Jialin Li, <i>National University of Singapore;</i> Jacob Nelson, <i>Microsoft Research;</i> Ellis Michael, <i>University of Washington;</i><br>Xin Jin, <i>Johns Hopkins University;</i> Dan R. K. Ports, <i>Microsoft Research</i> |

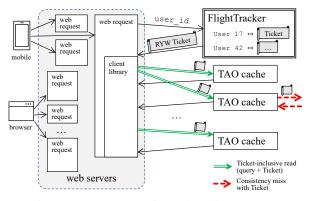

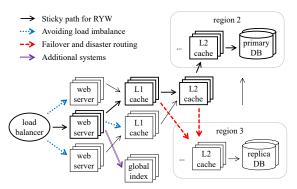

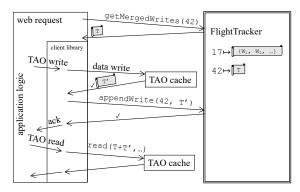

| FlightTracker: Consistency across Read-Optimized Online Stores at Facebook       407         Xiao Shi, Scott Pruett, Kevin Doherty, Jinyu Han, Dmitri Petrov, Jim Carrig, John Hugg, and Nathan Bronson, Facebook, Inc.                                                                                                                              |

| KVell+: Snapshot Isolation without Snapshots       425         Baptiste Lepers and Oana Balmau, University of Sydney; Karan Gupta, Nutanix Inc.; Willy Zwaenepoel, University of Sydney       425                                                                                                                                                    |

| Thursday, November 5                                                                                                                                                                                                                                                                                                                                 |

| Machine Learning 1                                                                                                                                                                                                                                                                                                                                   |

| Serving DNNs like Clockwork: Performance Predictability from the Bottom Up                                                                                                                                                                                                                                                                           |

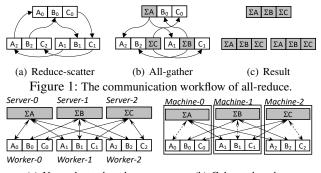

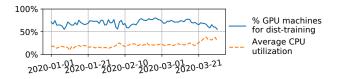

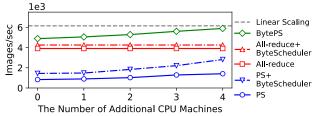

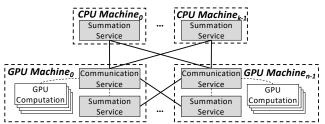

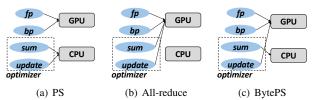

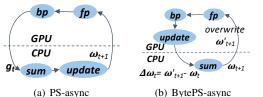

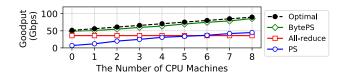

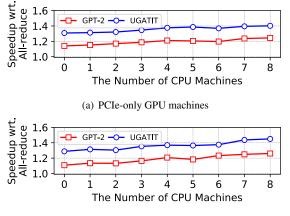

| A Unified Architecture for Accelerating Distributed DNN Training in Heterogeneous GPU/CPU Clusters 463<br>Yimin Jiang, <i>Tsinghua University and ByteDance;</i> Yibo Zhu, <i>ByteDance;</i> Chang Lan, <i>Google;</i> Bairen Yi, <i>ByteDance;</i><br>Yong Cui, <i>Tsinghua University;</i> Chuanxiong Guo, <i>ByteDance</i>                        |

| Heterogeneity-Aware Cluster Scheduling Policies for Deep Learning Workloads481Deepak Narayanan and Keshav Santhanam, Stanford University and Microsoft Research; Fiodar Kazhamiaka, Stanford1000000000000000000000000000000000000                                                                                                                    |

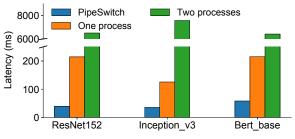

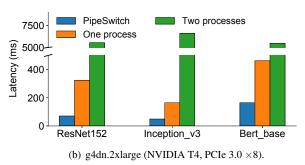

| PipeSwitch: Fast Pipelined Context Switching for Deep Learning Applications                                                                                                                                                                                                                                                                          |

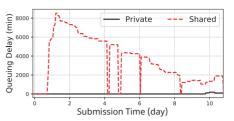

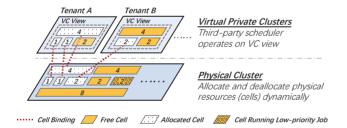

| <b>HiveD:</b> Sharing a GPU Cluster for Deep Learning with Guarantees                                                                                                                                                                                                                                                                                |

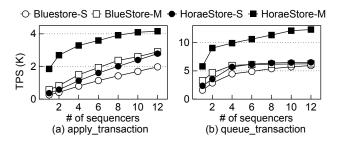

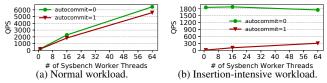

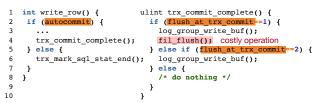

| Consensus Write Dependency Disentanglement with HORAE                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Xiaojian Liao, Youyou Lu, Erci Xu, and Jiwu Shu, <i>Tsinghua University</i>                                                                                                                                                                                                                                                                                                                                                        |

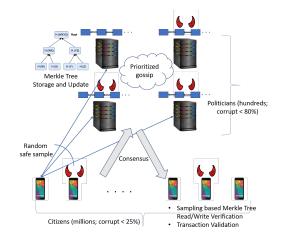

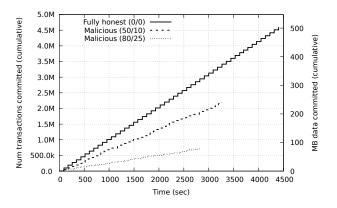

| Blockene: A High-throughput Blockchain Over Mobile Devices                                                                                                                                                                                                                                                                                                                                                                         |

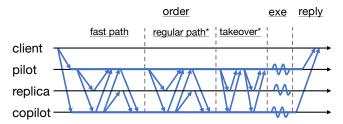

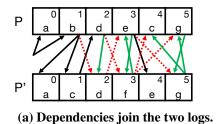

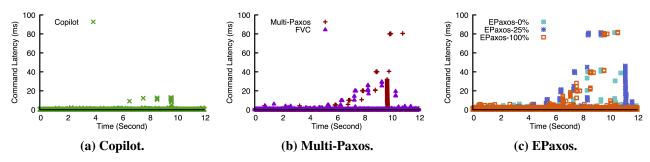

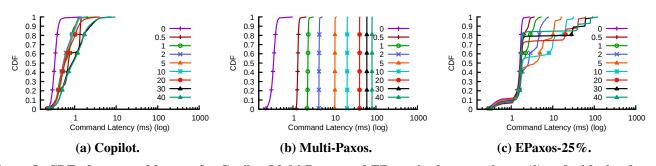

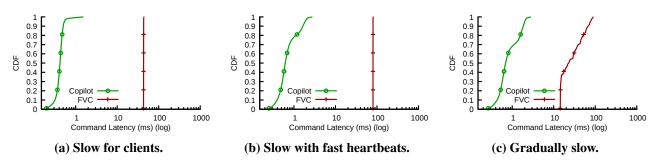

| Tolerating Slowdowns in Replicated State Machines using Copilots.       583         Khiem Ngo, Princeton University; Siddhartha Sen, Microsoft Research; Wyatt Lloyd, Princeton University                                                                                                                                                                                                                                         |

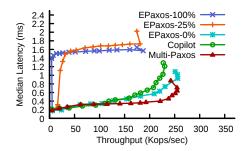

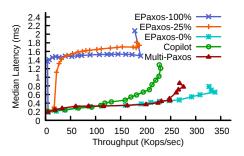

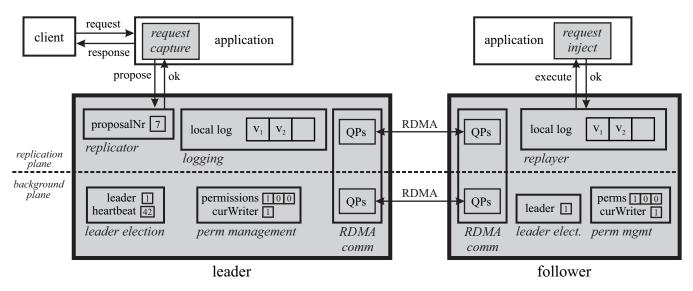

| Microsecond Consensus for Microsecond Applications                                                                                                                                                                                                                                                                                                                                                                                 |

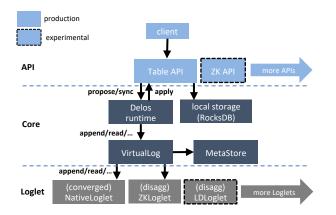

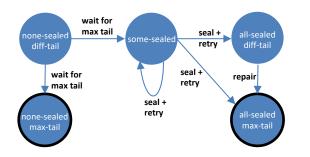

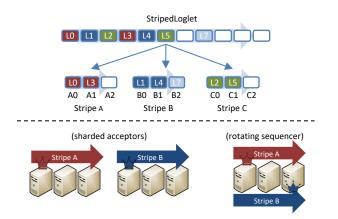

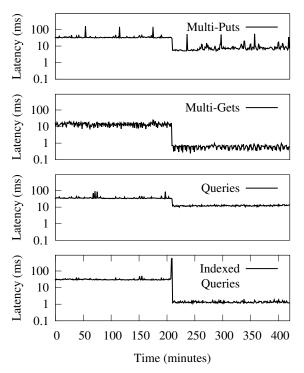

| <b>Virtual Consensus in Delos</b>                                                                                                                                                                                                                                                                                                                                                                                                  |

| <b>Byzantine Ordered Consensus without Byzantine Oligarchy</b>                                                                                                                                                                                                                                                                                                                                                                     |

| Bugs                                                                                                                                                                                                                                                                                                                                                                                                                               |

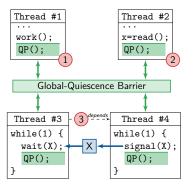

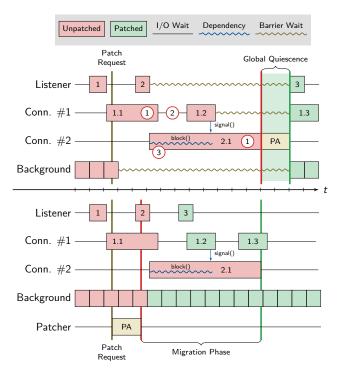

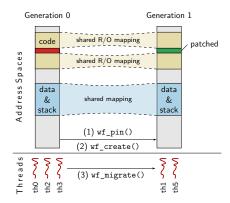

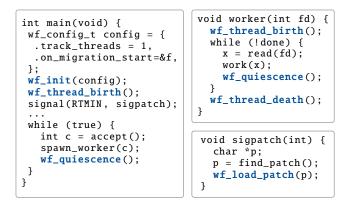

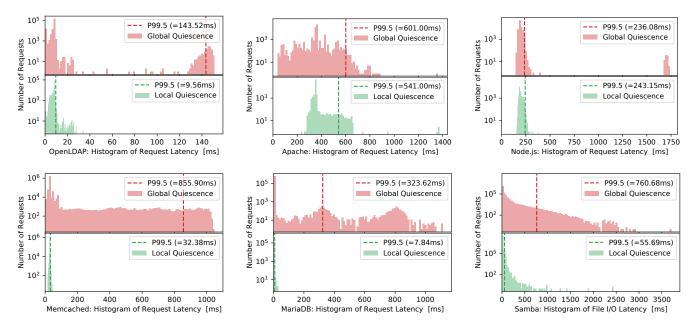

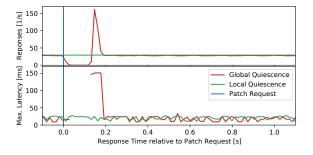

| <b>From Global to Local Quiescence: Wait-Free Code Patching of Multi-Threaded Processes</b>                                                                                                                                                                                                                                                                                                                                        |

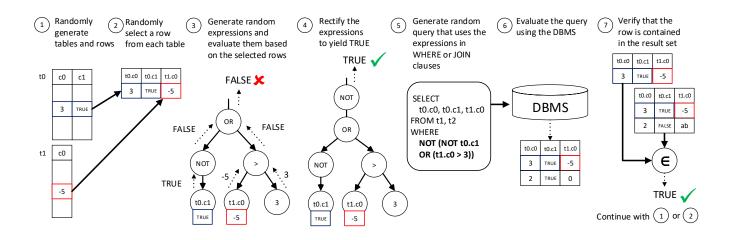

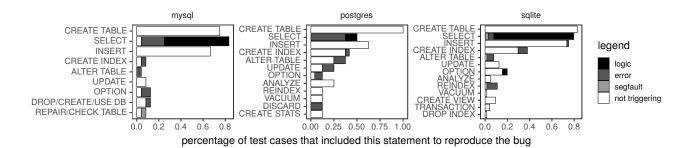

| Testing Database Engines via Pivoted Query Synthesis       667         Manuel Rigger and Zhendong Su, ETH Zurich                                                                                                                                                                                                                                                                                                                   |

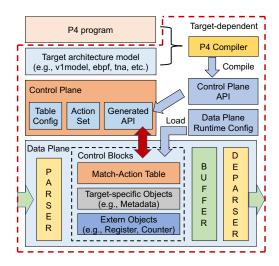

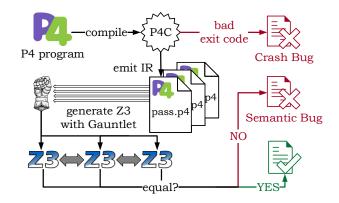

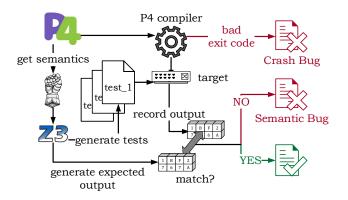

| Gauntlet: Finding Bugs in Compilers for Programmable Packet Processing                                                                                                                                                                                                                                                                                                                                                             |

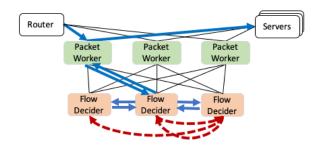

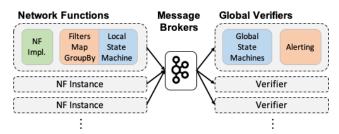

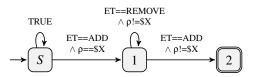

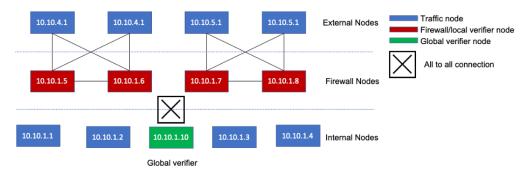

| <i>Aragog:</i> Scalable Runtime Verification of Shardable Networked Systems                                                                                                                                                                                                                                                                                                                                                        |

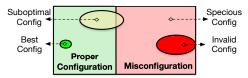

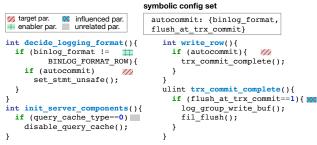

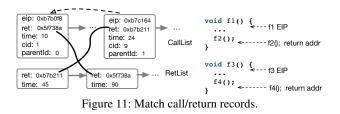

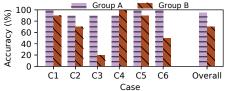

| Automated Reasoning and Detection of Specious Configuration in Large Systems with Symbolic Execution 719<br>Yigong Hu, Gongqi Huang, and Peng Huang, <i>Johns Hopkins University</i>                                                                                                                                                                                                                                               |

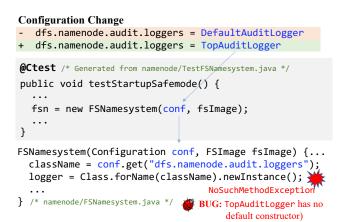

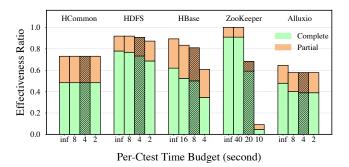

| <b>Testing Configuration Changes in Context to Prevent Production Failures</b>                                                                                                                                                                                                                                                                                                                                                     |

| Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                         |

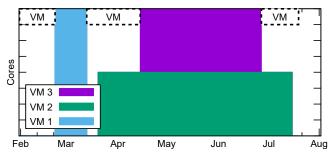

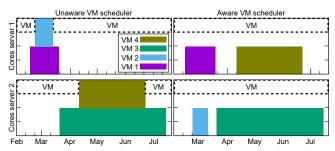

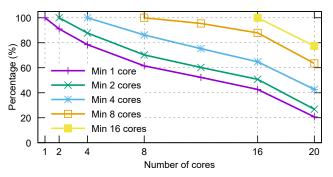

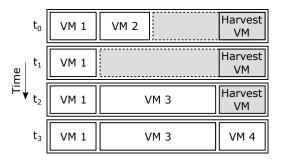

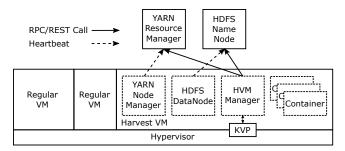

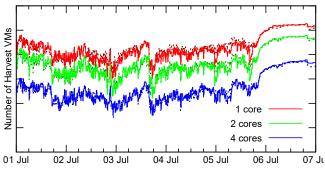

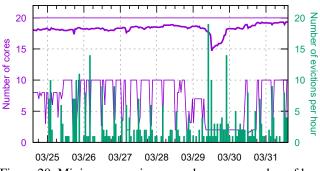

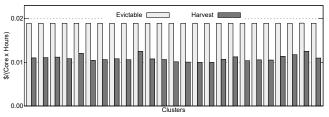

| <b>Providing SLOs for Resource-Harvesting VMs in Cloud Platforms.</b> 753<br>Pradeep Ambati, <i>University of Massachusetts, Amherst;</i> Íñigo Goiri, Felipe Frujeri, <i>Microsoft Azure and Microsoft Research;</i> Alper Gun and Ke Wang, <i>Google;</i> Brian Dolan, Brian Corell, Sekhar Pasupuleti, Thomas Moscibroda, Sameh Elnikety, Marcus Fontoura, and Ricardo Bianchini, <i>Microsoft Azure and Microsoft Research</i> |

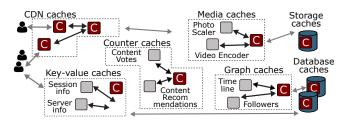

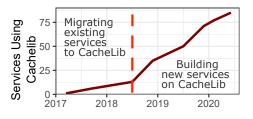

| The CacheLib Caching Engine: Design and Experiences at Scale                                                                                                                                                                                                                                                                                                                                                                       |

| Twine: A Unified Cluster Management System for Shared Infrastructure                                                                                                                                                                                                                                                                                                                                                               |

Chunqiang Tang, Kenny Yu, Kaushik Veeraraghavan, Jonathan Kaldor, Scott Michelson, Thawan Kooburat, Aravind Anbudurai, Matthew Clark, Kabir Gogia, Long Cheng, Ben Christensen, Alex Gartrell, Maxim Khutornenko, Sachin Kulkarni, Marcin Pawlowski, Tuomas Pelkonen, Andre Rodrigues, Rounak Tibrewal, Vaishnavi Venkatesan, and Peter Zhang, *Facebook Inc*.

**FIRM: An Intelligent Fine-grained Resource Management Framework for SLO-Oriented Microservices ...... 805** Haoran Qiu, Subho S. Banerjee, Saurabh Jha, Zbigniew T. Kalbarczyk, and Ravishankar K. Iyer, *University of Illinois at Urbana–Champaign*

### Friday, November 6

#### Machine Learning 2

Retiarii: A Deep Learning Exploratory-Training Framework

919

Quanlu Zhang, Zhenhua Han, Fan Yang, Yuge Zhang, Zhe Liu, Mao Yang, and Lidong Zhou, *Microsoft Research*

#### Hardware

| <b>FVM: FPGA-assisted Virtual Device Emulation for Fast, Scalable, and Flexible Storage Virtualization 955</b><br>Dongup Kwon, Department of Electrical and Computer Engineering, Seoul National University / Memory Solutions<br>Lab, Samsung Semiconductor Inc.; Junehyuk Boo and Dongryeong Kim, Department of Electrical and Computer<br>Engineering, Seoul National University; Jangwoo Kim, Department of Electrical and Computer Engineering, Seoul<br>National University / Memory Solutions Lab, Samsung Semiconductor Inc. |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

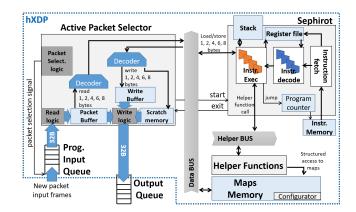

| hXDP: Efficient Software Packet Processing on FPGA NICs                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| <b>Do OS abstractions make sense on FPGAs?</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| $A = \{1, 2, 3, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5,$                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

#### Security

| Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Orchard: Differentially Private Analytics at Scale                                                                                                                                                                                                                                                                                                                                                                                                                                             | 65 |

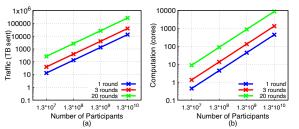

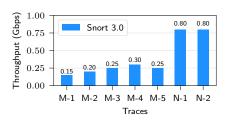

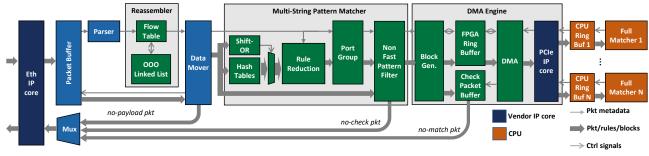

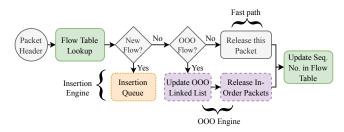

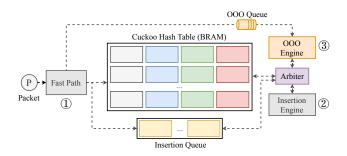

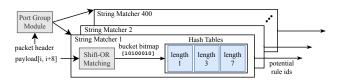

| Achieving 100Gbps Intrusion Prevention on a Single Server.       103         Zhipeng Zhao, Hugo Sadok, Nirav Atre, James C. Hoe, Vyas Sekar, and Justine Sherry, Carnegie Mellon University                                                                                                                                                                                                                                                                                                    | 83 |

| <b>DORY: An Encrypted Search System with Distributed Trust.</b> 110         Emma Dauterman, Eric Feng, Ellen Luo, Raluca Ada Popa, and Ion Stoica, University of California, Berkeley                                                                                                                                                                                                                                                                                                          | 01 |

| SafetyPin: Encrypted Backups with Human-Memorable Secrets       112         Emma Dauterman, UC Berkeley; Henry Corrigan-Gibbs, EPFL and MIT CSAIL; David Mazières, Stanford University                                                                                                                                                                                                                                                                                                         | 21 |

| Efficiently Mitigating Transient Execution Attacks using the Unmapped Speculation Contract                                                                                                                                                                                                                                                                                                                                                                                                     | 39 |

| Clusters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| <b>Predictive and Adaptive Failure Mitigation to Avert Production Cloud VM Interruptions.</b> 115<br>Sebastien Levy, Randolph Yao, Youjiang Wu, and Yingnong Dang, <i>Microsoft Azure;</i> Peng Huang, <i>Johns Hopkins University;</i> Zheng Mu, <i>Microsoft Azure;</i> Pu Zhao, <i>Microsoft Research;</i> Tarun Ramani, Naga Govindaraju, and Xukun Li, <i>Microsoft Azure;</i> Qingwei Lin, <i>Microsoft Research;</i> Gil Lapid Shafriri and Murali Chintalapati, <i>Microsoft Azure</i> | 55 |

| <b>Sundial: Fault-tolerant Clock Synchronization for Datacenters</b>                                                                                                                                                                                                                                                                                                                                                                                                                           | 71 |

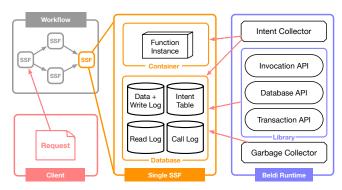

| Fault-tolerant and transactional stateful serverless workflows       118         Haoran Zhang, University of Pennsylvania; Adney Cardoza, Rutgers University–Camden; Peter Baile Chen, Sebastian       118         Angel, and Vincent Liu, University of Pennsylvania       118                                                                                                                                                                                                                | 87 |

| <b>Unearthing inter-job dependencies for better cluster scheduling</b>                                                                                                                                                                                                                                                                                                                                                                                                                         | 05 |

| RackSched: A Microsecond-Scale Scheduler for Rack-Scale Computers12Hang Zhu, Johns Hopkins University; Kostis Kaffes, Stanford University; Zixu Chen, Johns Hopkins University;12Zhenming Liu, College of William and Mary; Christos Kozyrakis, Stanford University; Ion Stoica, UC Berkeley; Xin Jin,12Johns Hopkins University12                                                                                                                                                             | 25 |

| <b>Thunderbolt: Throughput-Optimized, Quality-of-Service-Aware Power Capping at Scale</b>                                                                                                                                                                                                                                                                                                                                                                                                      |    |

Google LLC

#### Theseus: an Experiment in Operating System Structure and State Management

Kevin Boos Rice University Namitha Liyanage Yale University Ramla Ijaz Rice University Lin Zhong Yale University

#### Abstract

This paper describes an operating system (OS) called Theseus. Theseus is the result of multi-year experimentation to redesign and improve OS modularity by reducing the states one component holds for another, and to leverage a safe programming language, namely Rust, to shift as many OS responsibilities as possible to the compiler.

Theseus embodies two primary contributions. First, an OS structure in which many tiny components with clearly-defined, runtime-persistent bounds interact without holding states for each other. Second, an intralingual approach that realizes the OS itself using language-level mechanisms such that the compiler can enforce invariants about OS semantics.

Theseus's structure, intralingual design, and state management realize live evolution and fault recovery for core OS components in ways beyond that of existing works.

#### 1 Introduction

We report an experimentation of OS structural design, state management, and implementation techniques that leverage the power of modern safe systems programming languages, namely Rust. This endeavor was initially motivated by studies of state spill [16]: one software component harboring changed states as a result of handling an interaction from another component, such that their future correctness depends on said states. Prevalent in modern systems software, state spill leads to fate sharing between otherwise modularized and isolated components and thus hinders the realization of desirable computing goals such as evolvability and availability. For example, state spill in Android system services causes the entire userspace frameworks to crash upon a system service failure, losing the states and progress of all applications, even those not using the failed service [16]. Reliable microkernels further attest that management of states spilled into OS services is a barrier to fault tolerance [21] and live update [28].

Evolvability and availability of systems software are crucial in environments where reliability is necessary yet hardware redundancy is expensive or impossible. For example, systems software updates must be painstakingly applied without downtime or lost execution context in pacemakers [26] and space probes [25, 62]. Even in datacenters, where network switches are replicated for reliability, switch software failures and maintenance updates still lead to network outages [27,48]. On the quest to determine to what extent state spill can be avoided in OS code, we chose to write an OS from scratch. We were drawn to Rust because its ownership model provides a convenient mechanism for implementing isolation and zero-cost state transfer between OS components. Our initial OS-building experience led to two important realizations. First, mitigating state spill, or better state management in general, necessitates a rethinking of OS structure because state spill (by definition) depends on how the OS is modularized. Second, modern systems programming languages like Rust can be used not just to write safe OS code but also to statically ensure certain correctness invariants for OS behaviors.

The outcome of our experimentation is Theseus OS, which makes two contributions to systems software design and implementation. First, Theseus has a novel OS structure of many tiny components with clearly-defined, runtime-persistent bounds. The system maintains metadata about and tracks interdependencies between components, which facilitates live evolution and fault recovery of these components (§3).

Second, and more importantly, Theseus contributes the *in-tralingual* OS design approach, which entails matching the OS's execution environment to the runtime model of its implementation language and implementing the OS itself using language-level mechanisms. Through intralingual design, Theseus empowers the compiler to apply its safety checks to OS code with no gaps in its understanding of code behavior, and shifts semantic errors from runtime failures into compile-time errors, both to a greater degree than existing OSes. Intralingual design goes beyond safety, enabling the compiler to statically check OS semantic invariants and assume resource bookkeeping duties. This is elaborated in §4.

Theseus's structure and intralingual design naturally reduce states the OS must maintain, reducing state spill between its components. We describe Theseus's state management techniques to further mitigate the effects of state spill in §5.

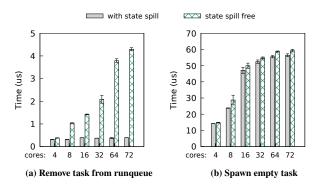

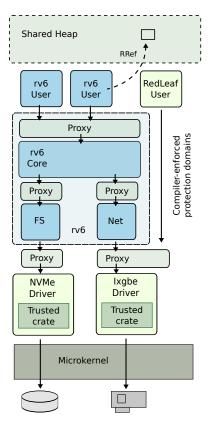

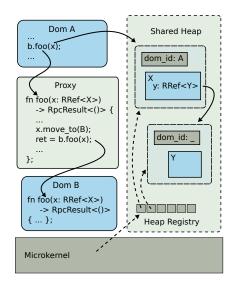

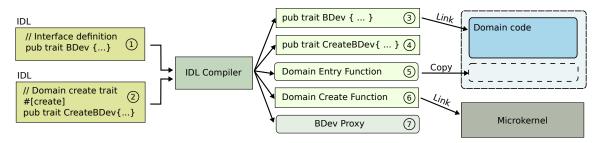

To demonstrate the utility of Theseus's design, we implement live evolution and fault recovery (for availability) within it (§6). With this, we posit that Theseus is well-suited for highend embedded systems and datacenter components, where availability is needed in the absence of or in addition to hardware redundancy. Therein, Theseus's limitations of being a new OS and needing safe-language programs have a lesser impact, as applications can be co-developed with the OS in an environment under a single operator's control. We evaluate how well Theseus achieves these goals in §7. Through a set of case studies, we show that Theseus can easily and arbitrarily live evolve core system components in ways beyond prior live update works, e.g., joint application-kernel evolution, or evolution of microkernel-level components. As Theseus can gracefully handle language-level faults (panics in Rust), we demonstrate Theseus's ability to tolerate more challenging transient hardware faults that manifest in the OS core. To this end, we present a study of fault manifestation and recovery in Theseus and a comparison with MINIX 3 of fault recovery for components that necessarily exist inside the microkernel. Although performance is not a primary goal of Theseus, we find that its intralingual and spill-free designs do not impose a glaring performance penalty, but that the impact varies across subsystems.

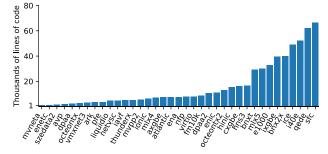

Theseus is currently implemented on x86\_64 with support for most hardware features, such as multicore processing, preemptive multitasking, SIMD extensions, basic networking and disk I/O, and graphical displays. It represents roughly four person-years of effort and comprises ~38000 lines of from-scratch Rust code, 900 lines of bootstrap assembly code, 246 crates of which 176 are first-party, and 72 unsafe code blocks or statements across 21 crates, most of which are for port I/O or special register access.

However, Theseus is far less complete than commercial systems, or experimental ones such as Singularity [33] and Barrelfish [8] that have undergone substantially more development. For example, Theseus currently lacks POSIX support and a full standard library. Thus, we do not make claims about certain OS aspects, e.g., efficiency or security; this paper focuses on Theseus's structure and intralingual design and the ensuing benefits for live evolution and fault recovery.

Theseus's code and documentation are open-source [61].

#### 2 Rust Language Background

The Rust programming language [40] is designed to provide strong type and memory safety guarantees at compile time, combining the power and expressiveness of a high-level managed language with the C-like efficiency of no garbage collection or underlying runtime. Theseus leverages many Rust features to realize an intralingual, safe OS design and employs the *crate*, Rust's project container and translation unit, for source-level modularity. A crate contains source code and a dependency manifest. Theseus does not use Rust's standard library but does use its fundamental core and alloc libraries.

Rust's *ownership* model is the key to its compile-time memory safety and management. Ownership is based on affine types, in which a value can be used at most once. In Rust, every value has an owner, e.g., the string value "hello!" allocated in L4 below is owned by the hello variable. After a value is moved, e.g., if "hello!" was moved in L5 from hello to owned\_string (L14), its ownership would be transferred and the previous owner (hello) could no longer use it.

```

fn main() {

let hel: &str;

let hello = String::from("hello!");

// consume(hello); // \longrightarrow "value moved" error in L6

let borrowed_str: &str = &hello;

hel = substr(borrowed_str);

// print!("{}", hel); // \rightarrow lifetime error

10

}

fn substr<'a>(input_str: &'a str) -> &'a str {

11

&input_str[0..3] // return value has lifetime 'a

12

13

}

fn consume(owned_string: String) {...}

14

```

When the owner's scope ends, e.g., at the end of a lexical block, the owned value is *dropped* (released) by virtue of the compiler inserting a call to its destructor. Destructors in Rust are realized by implementing the Drop trait for a given type,

in which a custom *drop handler* can perform arbitrary actions beyond freeing memory. On L8 above, the hello string falls

out of scope and is auto-deallocated by its drop handler. Values can also be *borrowed* to obtain references to them (L6), and the lifetime of those references cannot outlast the lifetime of the owned value. The syntax in L11 gives the name 'a to the lifetime of the input\_str argument, and specifies that the returned &str reference has that same lifetime 'a. That returned &str reference is assigned to hel in L7, which would result in a lifetime violation in L9 because hel would be used *after* the owned value it was originally borrowed from (hello) was dropped in L8. Rust's compiler includes a borrow checker to enforce these lifetime rules, as well as the core tenet of *aliasing XOR mutability*, in which there can be multiple immutable references or a single mutable reference to a value, but not both at once. This allows it to statically ensure memory safety for values on the stack and heap.

Theseus also extensively leverages Rust *traits*, a declaration of an abstract type that specifies the set of methods the type must implement, similar to polymorphic interfaces in OOP languages. Traits can be used to place *bounds* on generic type parameters. For example, the function fn print\_str<T: Into<String>>(s: T){ } uses the underlined trait bound to specify that its argument named s must be of any abstract type T that can be converted into a String.

#### 3 Theseus Overview and Design Principles

The overall design of Theseus specifies a system architecture consisting of many small distinct components, called *cells*, which can be composed and interchanged at runtime. A cell is a software-defined unit of modularity that serves as the core building block of the OS, much like their namesake of biological cells in an organism (no relation to Rust's std::cell). Theseus enables all software written in safe Rust, including applications and libraries, to coexist alongside the core OS components in a single address space (SAS) and execute at a single privilege level (SPL), building upon language-provided type and memory safety to realize isolation instead of hardware protection. Everything presented herein is written in Rust and runs in the SAS/SPL environment. Theseus follows three design principles:

- P1. Require *runtime-persistent* bounds for *all* cells.

- P2. Maximize the power of the language and compiler.

- P3. Minimize state spill between cells.

The remainder of this section describes how Theseus satisfies the first principle and why it matters, while §4 and §5 discuss the second and third principles, respectively.

#### 3.1 Structure of Runtime-Persistent Cells

Cells in Theseus have bounds that are clearly defined at implementation time and persist into and throughout runtime: a cell exists as a Rust *crate* at implementation time, a single object file at compile time, and a set of loaded memory regions with per-section bounds and dependency metadata at runtime. This applies to *all* cells, not just a select subset such as kernel extensions in monolithic and safe-language OSes or userspace servers in microkernels; there are no exemptions for components within a "base kernel" image. Explicit cell bounds identifiable at runtime are the foundation for strong data/fault isolation and state management in Theseus.

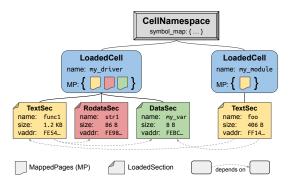

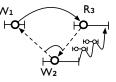

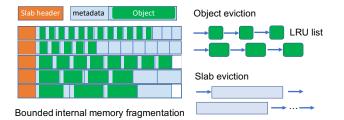

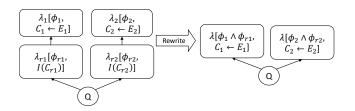

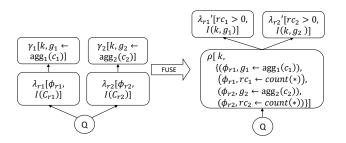

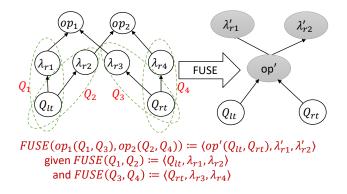

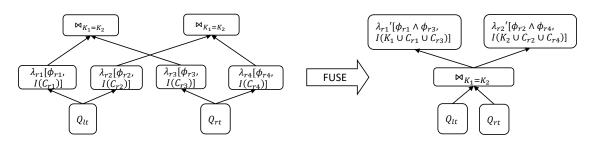

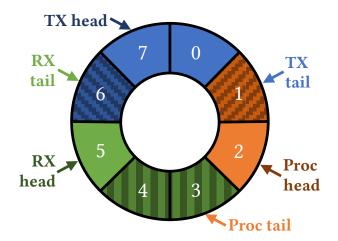

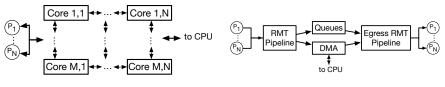

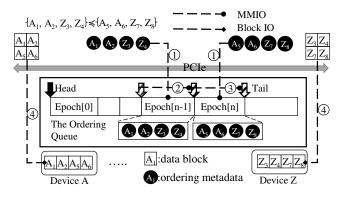

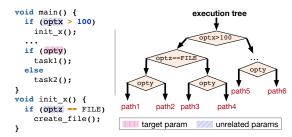

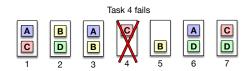

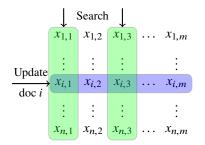

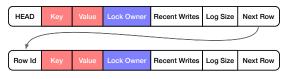

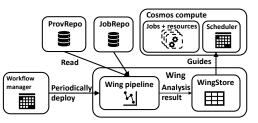

At runtime, Theseus loads and links all cells into the system on demand. Briefly, this entails finding and parsing the cell object file, loading its sections into memory, resolving its dependencies to write linker relocation entries, recursively loading any missing cells as needed, and adding new public symbols to a symbol map. In doing so, Theseus constructs detailed cell metadata, depicted in Figure 1, which is crucial knowledge for live evolution (§6.1) and fault recovery  $(\S6.2)$ . The set of loaded cells defines a CellNamespace, a true namespace containing all cells' public symbols, used to quickly resolve dependencies between cells. Each loaded cell node tracks its constituent sections and the memory regions ( $\S4.3.1$ ) that contain them. The sections in each cell correspond to those in its crate's object file, e.g., executable, read-only data, and read-write data sections. Each loaded section node tracks its size, location in memory, and bidirectional dependencies (incoming and outgoing); additional metadata exists to accelerate cell swapping and other system functions.

*Persistence of Cell Bounds Reduces Complexity:* Theseus's persistent cell bounds provide a consistent abstraction of OS structure throughout all phases of their existence. This reduces the complexity of a developer's mental model of the OS and simplifies fault recovery and evolution logic, as Theseus can introspect upon and manage its own code from the same cell-oriented viewpoint at runtime. The SAS/SPL environment augments this consistent view with *completeness*, in that everything from top-level applications and libraries to core kernel components are observable as cells. This enables Theseus to (*i*) implement a single mechanism, cell swapping, uniformly applicable to *any* cell, and (*ii*) jointly evolve cells from multiple system layers (e.g., applications and kernel components) in a safe manner.

Figure 1: Theseus constructs detailed metadata that tracks runtime cell bounds in memory and bidirectional, per-section dependencies in order to simplify cell swapping logic.

*Striking a Balance with Cell Granularity:* Theseus cells are elementary in their scope; we follow separation of concerns to split functionality into many tiny crates, letting unavoidable circular dependencies between them halt further decomposition. We do not use Rust's source-level module hierarchy in which one crate contains multiple Rust (sub)modules, as those module bounds are lost when the crate is built into an object file. Instead, we extract would-be modules into distinct crates, realizing hierarchy by organizing crates' source files into folders in Theseus's repository. This design offers both a programmer-friendly hierarchical view of source code and a simple system view of all cells as a flat set of distinct object files. It also strikes a balance between the complexity of needing to swap myriad tiny cells and the inefficiency and impracticality of swapping a large monolithic cell.

#### 3.2 Bootstrapping Theseus with the nano\_core

Theseus splits the compilation process at the linker stage, placing raw cell object files directly into the OS image such that linkage is deferred to runtime. From a practical standpoint, unlinked object files cannot run, so we must jump-start Theseus with the nano\_core. The nano\_core is a set of normal cells statically linked together into a tiny, executable "base kernel" image, comprising only components needed to bootstrap a bare-minimum environment that supports virtual memory and loading/linking object files. Because statically linking cells loses their bounds and dependencies, the nano\_core fully replaces itself at the final bootstrap stage by dynamically loading its constituent cells one by one, using augmented symbol tables and other metadata burned into the OS image at build time. This meets the requirement of runtime-persistent bounds for all cells, allowing the nano\_core to be safely unloaded after bootstrap.

#### **4 Power to the Language**

The second design principle Theseus follows is to leverage the power of the language by enabling the compiler to check safety and correctness invariants to the fullest extent possible. We term this approach *intralingual*, within the language, as it involves matching Theseus's execution environment to that of the language's runtime model, and implementing OS semantics fully within the strong, static type system offered by modern languages like Rust. This extends compiler-checked invariants (e.g., no dangling references) to *all* types of resources, not just those built into the language.

Intralingual design offers two primary benefits. First, it empowers the compiler to take over resource management duties, reducing the states the OS must maintain, which in turn reduces state spill and strengthens isolation. Second, it enables the compiler to apply safety checks with no gaps in its understanding of code behavior, approaching end-toend safety from applications to core kernel components and shifting semantic runtime errors into compile-time errors.

In contrast, traditional *extralingual* approaches rely on hardware protection and runtime checks to uphold invariants for safety, isolation, and correctness. These features are transparent to the compiler and require unsafe code. Even existing safe-language OSes [3, 13, 33, 44] have a gap between language-level safe code and the underlying unsafe core that implements the language's required abstractions as a black box. Below, we describe how Theseus closes this gap and opens up such black boxes to the compiler.

#### 4.1 Matching the Language's Runtime Model

The compiler for many languages, including Rust, expects that its output will become (part of) an executable that runs within one address space and privilege level, e.g., a single userspace process. Thus, the compiler cannot holistically observe or check the behavior of independently-compiled components that run in different address spaces or privilege levels.

To address this shortcoming, we tailor Theseus's OS execution environment to match Rust's runtime model: (*i*) only a single address space (SAS) exists and thus a single set of addresses is visible, for which Theseus guarantees a one-toone virtual-to-physical mapping; (*ii*) all code executes within a single privilege level (SPL), thus there is no other world or mode of execution; (*iii*) only a single allocator instance exists, matching the compiler's expectation that a global heap serves all allocation requests. Note that Theseus does support multiple arbitrary heaps within that single instance (§7.3).

#### 4.2 Intralingual OS Design

Matching the language's runtime model only allows the compiler to *view* all Theseus components. For the compiler to *understand* those components and apply its safety checks to them, we must implement them in a manner that exposes their safety requirements, invariants, and semantics to the compiler. As an aside, Theseus uses safe code to the fullest extent possible at all layers of the system, prioritizing safety over all else, e.g., convenience, performance. It only descends into unsafety when fundamentally unavoidable: executing instructions *directly* above hardware and select functions within Rust's foundational libraries, i.e., core and alloc.

Theseus goes beyond language safety to further empower the compiler to check our custom OS invariants as if they were built in. First, for each OS resource, Theseus identifies the set of invariants that prevent unsafety and incorrect usage. As the Rust compiler already checks myriad invariants for the usage of language-provided types and mechanisms, Theseus emplovs these existing mechanisms to allow its resource-specific invariants to be subsumed into those compiler invariants. For example, Theseus uses Rust's built-in reference types, such as &T and Arc<T> (Atomic Reference-Counted pointer), to share resources (e.g., memory regions, channel endpoints) across multiple tasks in a safe language-level manner, instead of extralingual sharing mechanisms like raw pointers or mapping multiple pages to the same frame. This eliminates possible use-after-free errors by subsuming resource mismanagement checks into the compiler's lifetime invariants.

Second, Theseus employs *lossless* interfaces for both external functions that export a resource's semantics and internal functions that implement those semantics. An interface is lossless if crossing it preserves all language-level context, e.g., an object's type, lifetime, or ownership/borrowed status. Furthermore, the *provenance* of that language-level context must be statically determinable, such that the compiler can authenticate that there was no broken link in the chain of calls and interface crossings when using a given resource. In other words, language-level knowledge must not be lost and then reconstituted extralingually. For example, invoking a system call in Linux loses the type and lifetime information of its arguments because they must be reduced to raw integer values to cross the user-kernel boundary.

#### **Ensuring Resource Cleanup via Unwinding**

One major invariant we enforce beyond default Rust safety is to prevent *resource leakage*, an acquired resource not being released even after no references to it remain. Although leakage does not violate safety, it is generally incorrect behavior. Theseus prevents resource leakage by (*i*) implementing all cleanup semantics in drop handlers ( $\S$ 2), a lossless languagelevel approach that allows the compiler to solely determine when it is safe to trigger resource cleanup, and (*ii*) employing *stack unwinding* to ensure acquired resources are always released in both normal and exceptional execution.

When tasks acquire resources in Theseus, they directly own objects representing those resources on their stack (§5.1). The Rust compiler tracks ownership of those objects to statically determine when a resource is dropped and, thus, where to insert its cleanup routine. Implementing all resource cleanup in only drop handlers frees developers from the burden of correctly ordering release operations or considering corner cases such as exceptional control flow jumps. Applying this to acquired locks allows Theseus to statically prevent many cases of deadlock: lock guards are auto-released during unwinding, and domain-specific locks automatically disable/re-enable preemption or interrupts, e.g., when modifying task runstates.

We implement Theseus's unwinder from scratch in Rust, with custom unwinding logic based on the DWARF standard [1] but independent from existing unwind libraries; thus, it works in core OS contexts without a standard library or allocation. Theseus starts the unwinder only upon a software or hardware exception or a request to kill a task; it does not interfere with normal execution performance, unlike garbage collectors. This prevents failed or uncooperative tasks from jeopardizing resource release and reclamation, strengthening fault isolation. The unwinder uses compiler-emitted information along with cell metadata to locate previous frames in the call stack, calculate and restore register values present during that frame, and discover and invoke cleanup routines or exception-catching blocks. Cell metadata even enables the unwinder to traverse through nonstandard stack frames for hardware-entered asynchronous calling contexts, e.g., interrupts or CPU exception handlers.

Theseus supports intralingual resource revocation in two forms. First, Theseus can forcibly revoke generic resources by killing and unwinding an uncooperative task. This avoids isolation-breaking undefined behavior by ceasing to execute a task once its assumptions of safe resource access no longer hold. Second, Theseus can cooperatively revoke reclaimable resources, such as in-memory caches and buffer pools, which express the possibility of resource absence within their type definition, e.g., using Option or weak references. This design unifies system-level and language-level resource actions to guarantee that revoked resources are freed exactly once.

#### 4.3 Examples of Intralingual Subsystems

We next describe how Theseus intralingually implements foundational OS resources, namely memory management and task management. Additional invariants, details, and examples, such as inter-task communication (ITC) channels, are omitted for brevity and available elsewhere [15].

#### 4.3.1 Memory Management

Theseus intralingually implements virtual memory via the MappedPages type of Listing 2, which represents a region of virtually-contiguous pages statically guaranteed to be mapped to (optionally contiguous) real physical frames. MappedPages is the fundamental, sole way to map and access memory in Theseus, and serves as the backing representation for stacks, heaps, and arbitrary memory regions, e.g., device MMIO and loaded cells. The design of MappedPages empowers the compiler's type system to enforce the following key invariants, extending Rust's memory safety checks to *all* OS memory regions, not just the compiler-known stack and heap.

**M.1:** The mapping from virtual pages to physical frames must be one-to-one, or bijective. This prevents aliasing (sharing) from occurring beneath the language, forcing all shared memory access in Theseus to use only language-level mechanisms, such as references (&MappedPages). In Theseus's SAS environment (§4.1), this is both possible and non-restrictive. In contrast, both conventional and existing safe-language OS

```

fn main() -> Result<()> {

let frames = get_hpet_frames()?;

let pages = allocate_pages(frames.count())?;

let mp_pgs = map(pages, frames, flags, pg_tbl)?;

let hpet: &HpetRegisters = mp_pqs.as_type(0)?;

print!("HPET device Vendor ID: {}", hpet.caps_id.read() >> 16);

let (sender. receiver) = rendezvous::new_channel::<MappedPages>():

let new_task = spawn_task(receiver_task, receiver)?;

10

11

sender.send(mp_pqs)?;

12

Ok(()) // `mp_pgs` not dropped, it was moved

13 }

14

fn receiver_task(receiver: Receiver<MappedPages>) -> Result<()> {

15

let mp: MappedPages = receiver.receive()?;

let hpet: &HpetRegisters = mp.as_type(0)?;

16

print!("Current HPET ticks: {}", hpet.main_counter.read());

17

Ok(()) // `mp` auto-dropped and unmapped here

18

19 }

20 struct HpetRegisters {

ReadOnly<u64>,

pub caps_and_id:

21

22

padding:

[u64, ...],

Volatile<u64>,

23

pub main_counter:

24

25 }

```

**Listing 1:** Example code that maps a memory region representing the HPET device, accesses the HPET vendor ID via MMIO, then spawns a new task and sends that memory region to it over a channel. The new task receives that memory region and uses it to read the HPET counter. This refers to code continued in Listing 2 and 3.

designs allow different virtual pages to map the same physical frame, an extralingual approach that renders sharing transparent to the compiler and thus uncheckable for safety.

We realize this invariant via the map() function (L26), which leverages type safety to take ownership of the allocated pages and frames in order to return a new MappedPages object. The lossless map() interface statically ensures the provenance of this relationship between AllocatedPages, AllocatedFrames, and MappedPages, guaranteeing they cannot be reused for duplicate mappings.

M.2: Memory must not be accessible beyond the mapped region's bounds. To access a memory region, one must use MappedPages methods like as\_type() (L45) or as\_slice() (L52) that overlay a statically-sized struct or dynamically-sized slice atop it; mutable versions exist, see M.4 below. The in-bounds invariant (L46) is checked dynamically unless elided when the size and offset are statically known, as in some MMIO cases. These access functions are lossless because they return sized types that preserve the lifetime relationship described below.

**M.3:** A memory region must be unmapped exactly once, only after there remain no outstanding references to it. MappedPages realizes its release and cleanup semantics only within its drop handler (L38), ensuring that a MappedPages object, such as mp in L15 of Listing 1, is unmapped in both normal execution (L18) and exceptional execution. Correspondingly, memory must not be accessible after it has been unmapped. The above access methods tie the lifetime of the re-typed borrowed reference & 'm T to the lifetime of its backing MappedPages memory region, allowing compiler lifetime checks to statically prevent use-after-free. As such, obtaining ownership of an overlaid struct is impossible by design, as

```

26 pub fn map(pages: AllocatedPages, frames: AllocatedFrames,

flags: EntryFlags, ...) -> Result<MappedPages> {

for (page, frame) in pages.iter().zip(frames.iter()) {

27

28

let mut pg_tbl_entry = pg_tbl.walk_to(page, flags)?

.get_pte_mut(page.pte_offset());

pg_tbl_entry.set(frame.start_addr(), flags)?;

29

30

Ok(MappedPages { pages, frames, flags })

31

32 }

33 pub struct MappedPages {

pages: AllocatedPages

35

frames: AllocatedFrames,

flags: EntryFlags.

36

37 }

38 impl Drop for MappedPages {

39

fn drop(&mut self) {

// unmap here: clear page table entry. invalidate TLB.

40

41

// AllocatedPages/Frames are auto-dropped and deallocated.

42

}

43 }

44 impl MappedPages {

45

pub fn as_type<'m, T>(&'m self, offset: usize) -> Result<&'m T> {

46

if offset + size_of::<T>() > self.size_in_bytes() {

return Error::OutOfBounds;

47

48

49

let typed_mem: &T = unsafe {

&*((self.pages.start_addr() + offset) as *const T) };

Ok(typed_mem)

50

51

}

52

pub fn as_slice<'m, T>(&'m self, offset: usize, count: usize)

-> Result<&'m [T]> { ... }

53 }

```

**Listing 2:** The basic MappedPages type (L33) exposes an interface (L44-53) for safely accessing its underlying memory region. The map() function (L26) maps a range of virtual pages to physical frames and returns a new MappedPages instance that represents that memory region. Sanity checks and details omitted for brevity.

that would lossily discard the above lifetime relationship.

**M.4:** A memory region must only be mutable or executable if mapped as such. We ensure this using dedicated types, MappedPagesMut and MappedPagesExec, that offer as\_type\_mut() and as\_function(), which statically prevents page protection violations as described elsewhere [15].

In summary, MappedPages bridges the semantic gap between the compiler's and OS's knowledge of memory, guaranteeing at compile time that unexpected invalid page faults cannot occur. Note that the necessary unsafe code in L49 is *innocuous* (see §8) as it merely indicates that the compiler cannot ensure the overlaid struct type has valid contents. Correctness of struct contents (e.g., HpetRegisters in L20) is unavoidably left to the developer. Regardless of developer mistakes, the compiler can still check that this unsafe code does not violate fault or data isolation because other invariants ensure it cannot produce dangling references (M.3) or access out-of-bounds addresses (M.2) beyond the reach of safe code. All other memory management code is safe down to the lowest level, where page table walks require extralingual code to accommodate hardware-defined page table formats.

#### 4.3.2 Task Management

While MappedPages is the center of intralingual memory management, the Task struct in Theseus is minimized in both content and significance. Rather, task management centers around intralingual functions that leverage a consistent set of generic type parameters to handle each stage of the task life-

```

54 pub trait TFunc<A,R> = FnOnce(A) -> R;

55 pub trait TArg = Send + 'static:

56 pub trait TRet = Send + 'static;

57 pub fn spawn_task<F,A,R>(func: F, arg: A, ...) -> Result<TaskRef>

where A: TArg, R: TRet, F: TFunc<A, R> {

let stack = alloc_stack(stack_size)?;

58

let mut new_task = Task::new(task_name, stack, ...)?;

let trampoline_offset = new_task.stack.size_in_bytes()

size_of::<usize>() - size_of::<RegisterCtx>();

60

let initial_context: &mut RegisterCtx = new_task.stack

61

.as_type_mut(trampoline_offset)?;

62

*initial_context = RegisterCtx::new(task_wrapper::<F,A,R>);

new_task.saved_stack_ptr = initial_context as *const RegisterCtx;

63

let func_arg: &mut Option<(F, A)> = new_task.stack.as_type_mut(0)?;

64

*func_arg = Some((func, arg));

65

Ok(TaskRef::new(new_task))

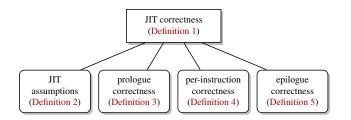

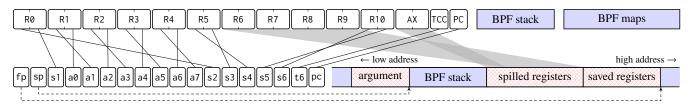

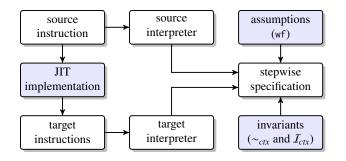

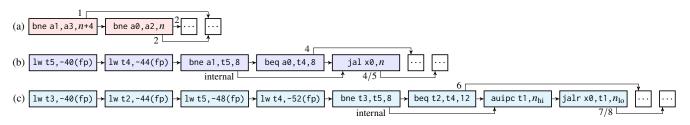

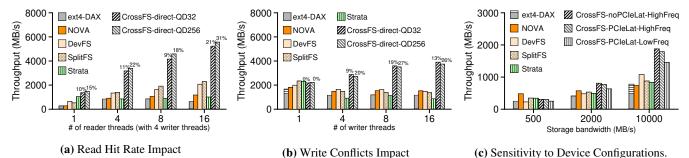

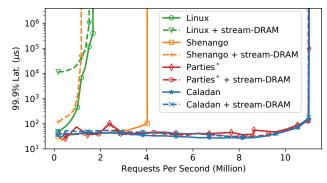

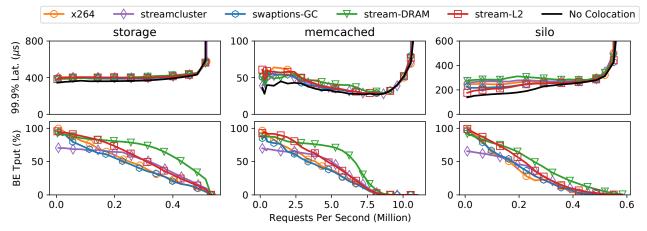

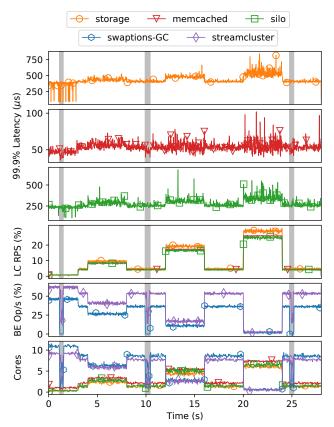

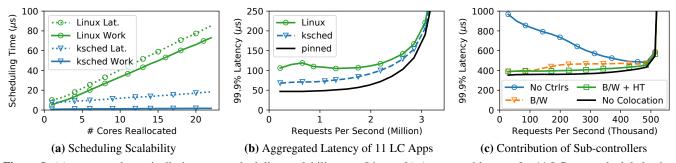

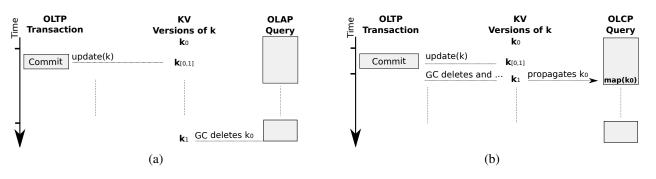

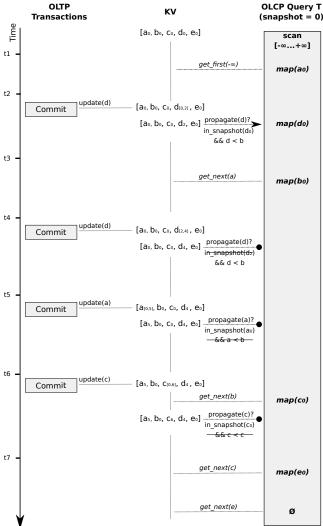

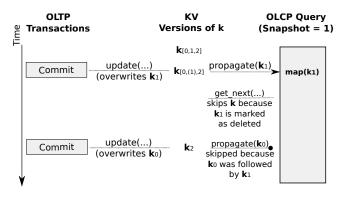

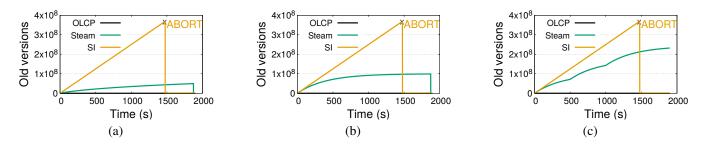

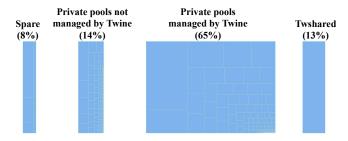

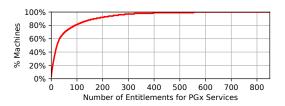

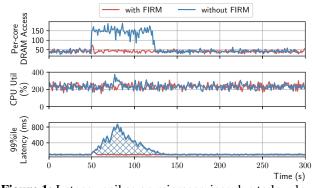

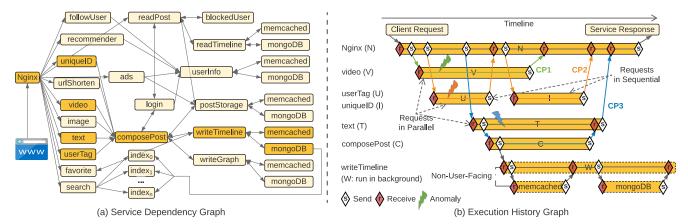

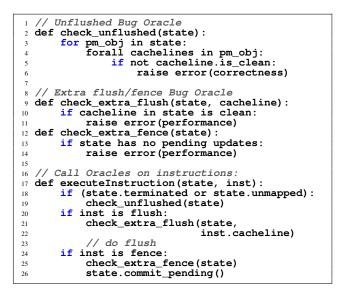

66